# WE DON'T NEED NO EXPLOITATION

Systematic Investigation of Process-based Rowhammer Exploitation

MARTIN HECKEL

Martin Heckel: We don't need no Exploitation, Systematic Investigation of Process-based Rowhammer Exploitation Academic supervisor: Prof. Dr. Florian Adamsky © November 22, 2022

# ABSTRACT

Rowhammer is a hardware vulnerability that enables an attacker to flip bits in memory without accessing them [1], resulting in the possibility of writing to memory locations that are not under the attacker's control. Rowhammer is based on spatial adjacency of the physical locations where the data are stored in the Dynamic Random-Access Memory (DRAM) Integrated Circuits (ICs) on the Dual In-line Memory Modules (DIMMs). Hence, exploitation is tricky and depends on multiple preconditions. Furthermore, there are mitigations like Target Row Refresh (TRR) implemented in current systems, so it is required to bypass these mitigations.

In the beginning, Rowhammer was known as a hardware vulnerability that could not be exploited reliably and was therefore seen as a rather academic problem. However, when Seaborn and Dullien [2] released an exploit that uses Rowhammer to flip bits in Page Table Entries (PTEs) to gain kernel-level privileges in memory, vendors started to release Basic Input/Output System (BIOS) updates to mitigate Rowhammer. Later, there were mitigations implemented directly in the DRAM hardware. Due to those mitigations, the initial Rowhammer exploits did not work anymore.

In the subsequent years, many publications related to Rowhammer mitigation approaches [3]–[5] and how to bypass these mitigations [6]–[20] were released. However, in many cases, the actual exploitability was not analyzed anymore. Often, only the number of bit flips or their offsets were analyzed: If a bit flips at offset n within a page, it is considered to be exploitable because it could be used for e.g. PTE exploitation if that page would store PTEs.

Current exploits rely on the page cache [11], PTEs [2], or on special memory mechanisms like Kernel Samepage Merging (KSM) [8] to escalate a user's privileges.

In this thesis, another approach based on the exploitation of memory mapped by processes (e.g. on the *stack* or *heap*) is introduced: If it is possible to use the memory mapping mechanisms of Linux in a way that a vulnerable page is mapped at a specified offset, it should be possible to execute a binary and afterwards flip a bit on that page which results, for example, in the inversion of a variable used in a condition. For example, that could be used to modify conditions on a binary with the Set User IDentification (SUID) bit set, e.g. by modifying *sudo* to permit access only when the password is incorrect.

Additionally, the automated testing system developed during my practical [21] and bachelor's [22] theses was improved. It was used on a new test setup to reproduce the results shown by Jattke, van der Veen, Frigo, et al. [17] on 60 DIMMs and to find DIMMs vulnerable to Rowhammer for further experiments. The number of bit flips identified in the experiments was much lower than described by the authors of the publication. Their results could not be reproduced.

With the experiments performed in this thesis, it is impossible to *remap* vulnerable pages at specified offsets reliably. For that reason, the approaches that were tested and tools that were

developed are presented. To the best of my knowledge, the approaches described in this thesis are not published yet if not noted otherwise. In detail, the following approaches, tools and results are introduced:

- The Hybridgrouping approach enables faster grouping of addresses by DRAM bank without the requirement to access Page Frame Numbers (PFNs) or use Transparent HugePages (THPs).

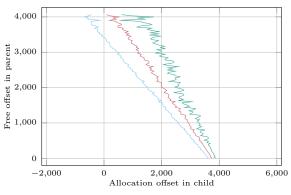

- It is shown that the vast majority (more than 97%) of the pages freed by a parent process are allocated by a child process spawned directly afterwards when Central Processing Unit (CPU) pinning is enabled.

- The offsets of the remappings between the parent and child process are analyzed.

- Alloctrace, a kernel module to dump the PFNs currently in the buddy allocator's orders and per-CPU lists of the different logical CPU cores, is introduced.

- MemCP, a multi-stage copying approach to reduce memory noise while creating a snapshot of the files provided by Alloctrace, is presented.

- Using Alloctrace and MemCP, the correlation between PFNs within the buddy allocator at different times and within the parent and child process is analyzed.

## ZUSAMMENFASSUNG

Rowhammer ist eine Hardware Schwachstelle, die es einem Angreifer ermöglicht, Bits im Dynamic Random-Access Memory (DRAM) zu flippen, ohne direkt darauf zuzugreifen [1]. Dadurch bekommt der Angreifer die Möglichkeit, effektiv in Speicherbereiche zu schreiben, auf die er keinen Zugriff hat. Rowhammer setzt räumliche Nähe von den physischen Speicherstellen, an denen die Daten auf den DRAM Integrated Circuit (IC) gespeichert werden, voraus. Aus diesem Grund ist das Ausnutzen von Rowhammer nicht trivial und hängt von mehreren Vorbedingungen ab. Zusätzlich gibt es auf aktuellen Systemen Mitigationen wie Target Row Refresh (TRR), die zuerst umgangen werden müssen.

Ursprünglich wurde Rowhammer als Hardware Schwachstelle, die nicht zuverlässig ausgenutzt werden kann, angesehen und aus diesem Grund als akademisches Problem behandelt. 2015 veröffentlichten Seaborn und Dullien [2] ein Exploit, in dem Rowhammer verwendet wird, um Bits in Page Table Entries (PTEs) zu flippen. Dadurch ist es einem Angreifer möglich, Speicherzugriff auf Kernel Ebene zu erlangen. Nach der Veröffentlichung dieses Exploits begannen Hersteller, Basic Input/Output System (BIOS) Updates bereitzustellen, die Rowhammer mitigieren. Später wurden entsprechende Mitigationen direkt in der DRAM Hardware implementiert. Durch diese Mitigationen funktionierten vorher veröffentlichte Exploits nicht mehr.

In den folgenden Jahren gab es viele Veröffentlichungen zu Rowhammer Mitigationen [3]–[5] und Möglichkeiten, diese zu umgehen [6]–[20]. In vielen Fällen wurde allerdings die tatsächliche Möglichkeit zum Exploiten nicht untersucht. Häufig wurde nur die Anzahl der Bit Flips sowie deren Offset analysiert: Wenn ein Bit an Offset n innerhalb einer Page flippt, wird es als exploitbar betrachtet, wenn es für z. B. PTE Exploitation verwendet werden könnte, sofern PTEs in der Page gespeichert wären.

Aktuelle Exploits nutzen den Page Cache [11], PTEs [2], oder besondere Mechanismen zur Speicherverwaltung wie Kernel Samepage Merging (KSM) [8] aus, um die Berechtigung eines Benutzers auszuweiten.

Im Rahmen dieser Masterarbeit wird ein anderer Ansatz zum Exploiten des Speichers, der von normalen Prozessen alloziert wird (z. B. auf dem Stack oder Heap), vorgestellt. Sofern es möglich ist, die Mechanismen zur Speicherverwaltung in Linux so zu nutzen, dass eine anfällige Page innerhalb des Kindprozesses an einem bestimmten Offset gemappt wird, sollte es möglich sein, den Bit Flip anschließend erneut zu provozieren. Somit tritt der Speicherfehler in der Page des Kindprozesses auf. Dadurch kann der Programmablauf des Kindprozesses manipuliert werden, indem eine in einer Bedingung verwendete Variable modifiziert wird. Dieser Ansatz könnte auf ausführbare Dateien, bei denen das Set User IDentification (SUID) Bit gesetzt ist, angewandt werden, z. B. um sudo so zu manipulieren, dass nur Zugriff gewährt wird, wenn das eingegebene Passwort nicht korrekt ist.

Zusätzlich werden einige Verbesserungen an dem automatisierten Testsystem, das im Rahmen meiner Praxisarbeit [21] und Bachelorarbeit [22] vorgestellt wurde, beschrieben. Das Testsystem wurde anschließend benutzt, um die Ergebnisse von Jattke, van der Veen, Frigo u. a. [17] auf 60 Dual In-line Memory Modules (DIMMs) zu evaluieren. Dadurch sollten außerdem DIMMs gefunden werden, die sehr anfällig für Rowhammer sind und in weiteren Experimenten verwendet werden können. Die Anzahl der im Rahmen dieser Experimente identifizierten Bit Flips war deutlich niedriger als von den Autoren beschrieben. Aus diesem Grund konnten die veröffentlichten Ergebnisse nicht reproduziert werden.

Mit den Experimenten, welche in dieser Arbeit vorgestellt werden, ist es nicht möglich, anfällige Pages stabil zu remappen, sodass diese immer an einem spezifizierten Offset innerhalb des Kindprozesses gemappt werden. Stattdessen werden die Ansätze und Programme, die im Rahmen dieser Masterarbeit erstellt und evaluiert wurden, vorgestellt. Sofern nicht anders angegeben ist mir zum jetzigen Zeitpunkt nicht bekannt, dass die in dieser Masterarbeit vorgestellten Ansätze bereits veröffentlicht wurden. Im Detail werden die folgenden Ansätze, Tools und Ergebnisse vorgestellt:

- Der Hybridgrouping Ansatz ermöglicht es, virtuelle Adressen schnell auf Basis der *Bank* zu gruppieren, auf der diese im physisch im DRAM liegen. Dieser Ansatz funktioniert ohne Zugriff auf Page Frame Numbers (PFNs) oder die Verwendung von Transparent HugePages (THPs).

- Es wird gezeigt, dass der Großteil (mehr als 97%) der Pages, die von einem Elternprozess freigegeben werden, von einem direkt danach gestarteten Kindprozess erneut alloziert werden, sofern Central Processing Unit (CPU) Pinning aktiviert ist.

- Die Offsets der Remappings zwischen dem Eltern- und Kindprozess werden analysiert.

- Alloctrace, ein Kernelmodul zum Ausgeben der PFNs, die sich aktuell auf den verschiedenen Ordnungen des Buddy Allocators oder in den per-CPU Listen der verschiedenen logischen CPU Kerne befinden, wird vorgestellt.

- MEMCP, ein Ansatz zum mehrstufigen Kopieren, wird vorgestellt. Durch diesen Ansatz ist es möglich, die Störungen durch Speicherzugriffe zu reduzieren, während eine Kopie der von Alloctrace bereitgestellten Dateien durchgeführt wird.

- Unter Verwendung von AllocTrace und MemCP wird die Korrelation zwischen den PFNs, die vom Eltern- oder Kindprozess alloziert wurden, und den PFNs, die sich zu verschiedenen Zeitpunkten in den Listen des Buddy Allocators befinden, untersucht.

We don't demand solid facts!

What we demand is a total absence of solid facts.

I demand that I may or may not be Vroomfondel!

— Vroomfondel [23]

## ACKNOWLEDGEMENTS

While performing the experiments and writing this master's thesis, I received much support and assistance.

While the experiments were performed, there were many situations where the results looked not as expected, and I could not explain them. Especially but not only in these situations, I had the possibility to discuss the experiments, results, possible explanations, etc., with several people. At this point, I want to thank Prof. Dr. Florian Adamsky, Adrian Märtins, and Dominik Thalhammer for the many discussions we had in the last months. Lots of the approaches presented in this thesis emerged during these discussions.

In order to increase the quality of the results, there were some experiments for which measurements on additional systems were useful to evaluate the hypotheses more completely. I want to thank Prof. Dr. Florian Adamsky, Sebastian Pahl, and Dominik Thalhammer for performing some of the experiments on their systems and, thereby, providing more data to evaluate the hypotheses.

In this thesis, there is an experiment where 60 Double Data Rate 4 (DDR4) Dual In-line Memory Modules (DIMMs) were tested for Rowhammer susceptibility. I want to thank the research group System and Network Security (SNS) and the Institute for Information Systems (iisys) at Hof University for providing the hardware<sup>1</sup> that made this experiment possible.

Finally, I want to thank Nico Bretschneider, Johanna Heckel, Michelle Madeline Krebs, Adrian Märtins, Angelina Scheler and Peter Siedentopf for proofreading this thesis.

<sup>&</sup>lt;sup>1</sup>Two computers and 60 DDR4 DIMMs

# CONTENTS

| Li       | st of                  | Figures                                      | Ι   |

|----------|------------------------|----------------------------------------------|-----|

| Li       | st of                  | Tables                                       | II  |

| Li       | $\operatorname{sting}$ | ÇS                                           | III |

| A        | bbre                   | viations                                     | IV  |

| 1        | Inti                   | roduction                                    | 1   |

|          | 1.1                    | Objective of this Thesis                     | 1   |

|          | 1.2                    | Structure of this Thesis                     | 2   |

| <b>2</b> | Bac                    | ekground                                     | 3   |

|          | 2.1                    | Memory Allocation in Linux                   | 3   |

|          | 2.2                    | DRAM                                         | 7   |

|          | 2.3                    | CPU Cache                                    | 10  |

|          | 2.4                    | DRAM Address Functions                       | 11  |

|          | 2.5                    | Rowhammer                                    | 12  |

| 3        | Flip                   | oper on DDR4                                 | 15  |

|          | 3.1                    | Automated Test Setup                         | 15  |

|          | 3.2                    | BlackSmith Experiment                        | 18  |

| 4        | Exp                    | ploitation Approach                          | 20  |

|          | 4.1                    | Hybrid Grouping                              | 21  |

|          | 4.2                    | Page Reallocation                            | 29  |

|          |                        | 4.2.1 Reallocation Percentage of freed Pages | 29  |

|          |                        | 4.2.2 Offsets of reallocated Pages           | 31  |

|          |                        | 4.2.3 Tracing of Pages                       | 34  |

### Contents

| 5  | Related Work | 40 |

|----|--------------|----|

| 6  | Future Work  | 42 |

| 7  | Conclusion   | 44 |

| Re | eferences    | 46 |

# LIST OF FIGURES

| 1  | Simplified presentation of the mapping between virtual and physical addresses |    |

|----|-------------------------------------------------------------------------------|----|

|    | using page tables                                                             | 4  |

| 2  | Detailed presentation of address resolution using page tables                 | 5  |

| 3  | Overview of the memory management of Linux                                    | 7  |

| 4  | Single DRAM cell                                                              | 7  |

| 5  | Array of DRAM cells                                                           | 8  |

| 6  | DRAM Architecture: Bank                                                       | 9  |

| 7  | Dynamic Random-Access Memory (DRAM) Architecture overview                     | 10 |

| 8  | Some typical patterns for Rowhammer exploitation                              | 13 |

| 9  | Exploitation approach for attacking process memory                            | 21 |

| 10 | Overview of the HybridGrouping approach                                       | 23 |

| 11 | Example of the usage of bank sequences                                        | 25 |

| 12 | Remapping offsets between parent and child process                            | 33 |

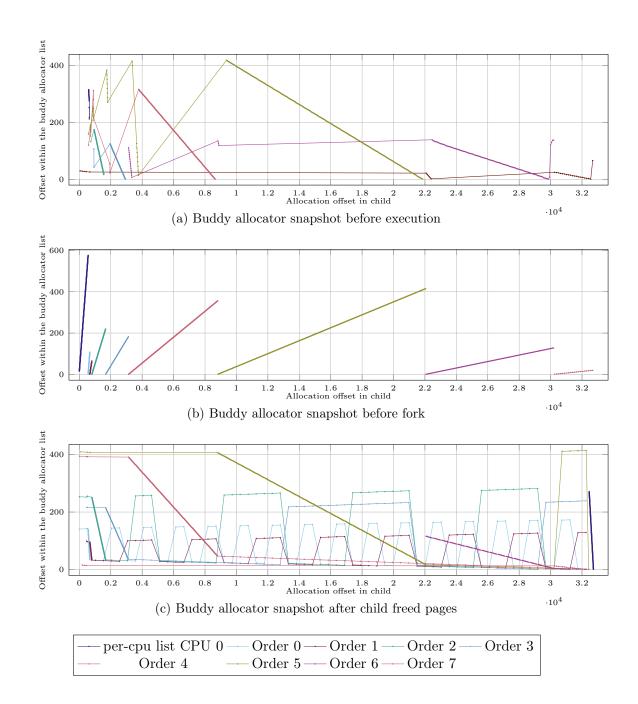

| 13 | Offsets within the buddy allocator (parent process)                           | 37 |

| 14 | Offsets within the buddy allocator (child process)                            | 38 |

# LIST OF TABLES

| 1 | Number of Bit Flips found within 6 hours by the BlackSmith PoC without flipper | 19 |

|---|--------------------------------------------------------------------------------|----|

| 2 | Resolution of the rdtscp counter on different systems                          | 28 |

| 3 | Remapping percentage of freed pages                                            | 31 |

# LISTINGS

| 1 | Example of a file describing an experiment for the test setup | 16 |

|---|---------------------------------------------------------------|----|

| 2 | Lines to enable the experiment created before                 | 18 |

## **ABBREVIATIONS**

BIOS Basic Input/Output System

CPU Central Processing Unit

DDR3 Double Data Rate 3

DDR4 Double Data Rate 4

**DIMM** Dual In-line Memory Module

**DoS** Denial of Service

**DRAM** Dynamic Random-Access Memory

**ECC** Error Correction Code

**EEPROM** Electrically Erasable Programmable Read-Only Memory

IC Integrated Circuit

iisys Institute for Information Systems

IPC Inter-Process Communication

KSM Kernel Samepage Merging

KVM Kernel-based Virtual Machine

L1 Level 1

L2 Level 2

L3 Level 3

LLC Last Level CacheMAC Media Access ControlMC Memory Controller

MMU Memory Management Unit

NIC Network Interface Controller

OOM Out Of Memory osOperating System **PFN** Page Frame Number **PGD** Page Global Directory **PUD** Page Upper Directory **PMD** Page Middle Directory PTE Page Table Entry PoC Proof of Concept

RDMA Remote Direct Memory Access

SGX Software Guard Extensions

SMASH Synchronized MAny-Sided Hammering

**SNS** System and Network Security

SPD Serial Presence DetectSUID Set User IDentificationTHP Transparent HugePage

TLB Translation Lookaside Buffer

# Abbreviations

TRR Target Row RefreshTSC TimeStamp Counter

**pTRR** pseudo Target Row Refresh

VM Virtual Machine

## 1 Introduction

In 2014, Kim, Daly, Kim, et al. [1] demonstrated that many Double Data Rate 3 (DDR3) Dual In-line Memory Modules (DIMMs) are susceptible to memory errors. 110 out of the 129 DDR3 DIMMs tested were prone to errors induced by specific access patterns. It was possible to flip bits in memory without accessing them by reading other data from memory. They mentioned that such disturbance errors can be exploited but did not provide a Proof of Concept (PoC). Therefore, their results were not relevant for real-world use cases and were seen as an academic problem then. Later, the attack they introduced got known as Rowhammer.

One year later, Seaborn and Dullien [2] provided a PoC that exploits Rowhammer to flip bits in Page Table Entries (PTEs), thereby gaining kernel-level privileges in memory. It was shown that Rowhammer was not a purely academic topic anymore but had an impact on the everyday usage of Dynamic Random-Access Memory (DRAM), which is an integral part of many computer systems.

In the following years, the topic of Rowhammer gained more attention, and many publications presented new offensive [6]–[20] and defensive [3]–[5] approaches. It was shown that Rowhammer could be exploited from the JavaScript code running in a browser [6], [19], on mobile devices [9], across different Virtual Machines (VMs) [8], and over the network [12], [13]. It was also shown that Rowhammer could be used to read memory without accessing it [16].

#### 1.1 Objective of this Thesis

In the scope of my practical [21] and bachelor's [22] theses, two novel attacks that increase the amount of bit flips found in a given time by a hundredfold were introduced. Due to a lack of Double Data Rate 4 (DDR4) Hardware susceptible to Rowhammer at the time of writing, these attacks were evaluated on DDR3 only. The market share of DDR3 DRAM has decreased strongly in the last few years. Therefore the relevance of the evaluation described in these theses has also decreased. For that reason, one objective of this thesis is to use a system with DDR4 DRAM and repeat the evaluation on that system. In the first step, the results presented in [17] should be reproduced in order to find DIMMs that are susceptible to Rowhammer.

Some approaches exploit the code pages stored in the page cache [11], use PTEs [2], or specific memory mechanisms like Kernel Samepage Merging (KSM) [8] to escalate a user's privileges using Rowhammer. However, to the best of my knowledge, there is no exploitation technique that flips bits in the memory allocated by normal processes to achieve a local privilege escalation.

#### 1 Introduction

The following research questions are addressed in this thesis:

- **RQ 1**: Can the results presented in [17] be reproduced on 60 DDR4 DIMMs?

- **RQ 2**: Is it possible to exploit Rowhammer to modify the memory mapped by processes by using the memory mapping mechanisms of the Linux kernel?

Because none of the tested systems with DDR4 DRAM is susceptible to Rowhammer (there are a couple of bit flips on some systems, but not enough to perform a severe evaluation), the evaluation of the approaches introduced in [21], [22] is not performed. The partly automated experimental setup and the results of the search for affected modules are presented in this thesis.

Due to time limitations, it was not possible to get the complete process-based exploitation approach running in the scope of this thesis. Therefore, the current state is described instead. A new approach of mapping virtual addresses to physical *banks* in memory is introduced. Additionally, some insights into the memory allocation done when a process starts are shown.

#### 1.2 STRUCTURE OF THIS THESIS

At the beginning of this thesis, some essential background topics are explained in Section 2.

Afterwards, the experimental setup and the results of the measurements to find vulnerable DDR4 modules are described in Section 3. Additionally, some experiments on the granularity of the TimeStamp Counters (TSCs) of the CPUs are described.

Section 4 describes the approach of exploiting Rowhammer using the memory allocation of normal processes in detail. As a part of that, a new approach of mapping virtual addresses to physical bank numbers is introduced. Next, the internal mechanisms of page allocation are analyzed in detail.

A short overview of related publications is shown in Section 5. Section 6 contains some ideas that could be researched in the future. Finally, in Section 7, this thesis is concluded.

If not noted otherwise, the figures, listings and tables in this thesis were created by myself.

This section contains background information required to understand the rest of this thesis. The information within this section refer to the amd64 architecture.

#### 2.1 Memory Allocation in Linux

In most modern Operating Systems (OSs), memory is virtualized. Therefore, the addresses used by applications or the kernel are not the same addresses where the data is stored [24].

With virtualized addresses, it is not required to split the physical address space, shared among all processes and the kernel, so that spatial requirements are met. When an array (or a string) is allocated in a low-level programming language like C, the addresses have to be in a continuous block to address the array's single elements by using the start address and the offset. Even though high-level programming languages abstract that fact from the programmer, they rely on the same principles as C, so they also require continuous blocks of virtual memory.

Another advantage of virtualized addresses is that they can be used for *paging* [25], so it is possible to move some blocks of memory to the hard drive when there is not much free physical memory. Then, if the block is accessed the next time, it can be loaded from the hard drive and restored to physical memory before access. That procedure is implemented in the kernel and transparent to the process that accesses the memory.

Virtual memory requires some kind of translation between virtual and physical addresses. Because these translations have to be calculated somehow, memory addresses are not handled one by one where each byte is mapped individually but in blocks, called *pages*, to reduce the required number of mapping resolution operations. There is a tradeoff between the required number of calculations for address resolution and the granularity in which memory can be mapped. The *page size* defines the size of blocks managed by one mapping and specifies the granularity vs expense tradeoff. On x86 Linux, it is defined to be 4 KiB.

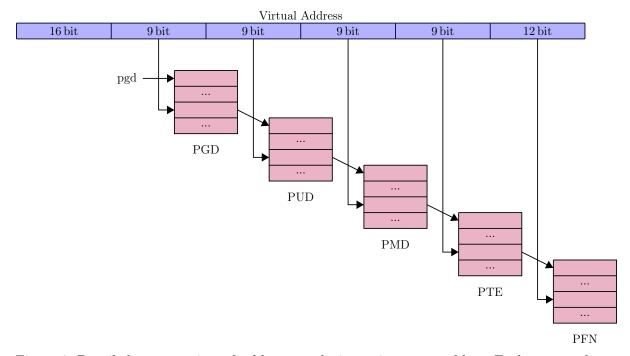

In order to map virtual addresses to physical addresses, page tables consisting of PTEs are used. One PTE stores the mapping between the virtual address and the physical address of a page. In order to use addresses within a page, the page mapping is resolved using PTEs first. Afterwards, the offset of the address within the page is taken from the virtual address. Therefore, the offset for the virtual and the physical address is always the same. The base address of the physical address is called Page Frame Number (PFN), as shown in Figure 1.

In contrast to the simplified version of the mapping of pages shown in Figure 1, the process is more complex, and there are multiple layers of tables [24]: Page Global Directory (PGD), Page Upper Directory (PUD), Page Middle Directory (PMD), and PTE. A virtual address is split into

Figure 1: Simplified presentation of the mapping between virtual and physical addresses using page tables. Note that the virtual address's last 12 bit (three hexadecimal digits) are always zero. That is the case because the page size is 4 KiB which requires 12 bit for addressing. The address depicted as the physical address is the PFN (it does not contain that last 12 bit). The physical address is calculated using the PFN and appending the last 12 bit from the virtual address (0x2042 would be mapped to 0x3ef042 in the depicted example). The image is based on [26].

several parts that correspond to the offset within the corresponding layer of the page tables, as shown in Figure 2.

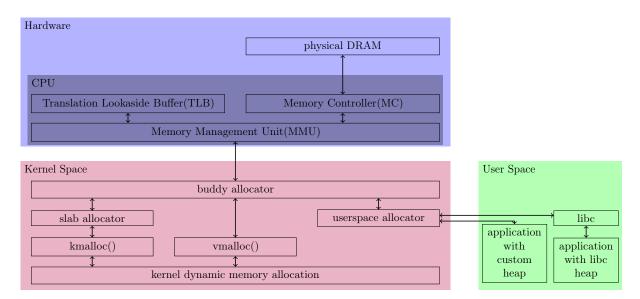

The calculation of the physical address mapped to a virtual address is done by the Memory Management Unit (MMU), a part of the Central Processing Unit (CPU) in many modern systems. On the other hand, the translation between physical addresses and spatial locations, which are used to address data in DRAM (called *spatial address* in this thesis), is done by the Memory Controller (MC).

Because calculating a physical address from a virtual address is rather complex, the Translation Lookaside Buffer (TLB) is used to cache the last resolved mappings. Otherwise, it would be required to perform a complete lookup, as shown in Figure 2, for each memory access. According to [24], processes tend to have a locality of references, e.g. many memory accesses are performed on a small number of pages. Therefore, using a TLB can decrease the number of mapping resolutions. The mapping for each accessed page is loaded from the TLB. Only when there is a TLB miss, so the mapping for the page is not cached, it is resolved using the procedure depicted in Figure 2.

There are some applications where a considerable amount of (optionally continuous) virtual memory is required, e.g. for loading the content of a file to a buffer. In order to reduce the number of pages that have to be mapped (and resolved), the last 9 bit of the mapping can be added to the offset part, e.g. there is only one mapping for  $2^9 = 512$  pages. The offset within that page is not 12 bit but 21 bit, so the page has a size of  $2^{21} = 2097152$  B, equivalent to 2 MiB. These special pages are called Transparent HugePage (THP). If not specified otherwise, they are allocated automatically by the kernel if a memory mapping is big enough that the usage of a THP is considered beneficial. It should be noted that the THP, due to an offset of 21 bit, has to be aligned properly in virtual and physical address space (e.g. the last 21 bit of the first address of the THP have to be 0, the THP has to be allocated on a 2 MiB border).

Figure 2: Detailed presentation of address resolution using page tables. Each process has a list of PGDs stored in  $mm\_struct->pgd$  and depicted as pgd in the figure. The first 16 bit of the virtual address are the sign extension and currently not used for address mapping [27]. The next 9 bit specify an entry in the list of PGDs. That entry references another list of PUDs. The following 9 bit of the virtual address specify a PUD which references a list of PMDs. The next 9 bit of the virtual address specify the entry in the list of PMDs, which references to a list of PTEs The next 9 bit specify an entry in the list of PTEs that references to a PFN. The last 12 bit of the virtual address specify the offset within the page specified by the PFN. The sizes of the separate parts were measured using the approach described in Section A.1.

Besides the implicit and automatic allocation of THP, it is possible to use madvise() [28] with the advice value  $MADV\_HUGEPAGE$  or  $MADV\_NOHUGEPAGE$  to explicitly use or not use THP for the specified address range. Because pages are not allocated at the time of calling mmap [29] but at the time of the first write access, they are directly allocated as THP if madvise() is called before first writing to them.

When a page is allocated, the kernel adds entries to the according structures within the page tables to make the mapping between a virtual and a physical address accessible. However, the physical page that should be mapped has to be selected before that is possible. Therefore, the kernel must keep track of which pages are currently free to allocate them.

In Linux, that is not implemented with a linear list of free pages but with the *buddy allocator* [24]. That buddy allocator handles lists of blocks of  $2^n$  pages, where n is called the *order* of the block. The buddy allocator on this system<sup>2</sup> uses orders 0 (blocks of 1 page) up to 10 (blocks of 1024 pages).

When all pages within an order are allocated (there are no free pages left), pages of a higher order can be split (e.g. one page of order 1 can be split into two pages of order 0). Both split blocks are marked as *buddies*. When both buddies are free at the same time, they will be merged again to a higher-order page. That principle can be chained over multiple orders (e.g. one page of order 8 is split into two pages of order 7, these two pages are split into 4 pages of order 6, two of those pages are split into four pages of order 5, etc.)

That approach brings the benefit of reduced fragmentation because the buddies of small allocations are merged again, resulting in bigger blocks of physically continuous pages available.

Because the buddy allocator is shared for the whole system (e.g. all logical CPUs access the same lists of free pages), the buddy allocator requires locking mechanisms to avoid multiple CPUs modifying the data structures simultaneously. In order to reduce that bottleneck, additional per-CPU lists of free pages are used as a cache between the page allocation mechanism and the buddy allocator.

When a page is freed, it is added to the per-CPU list accordingly, so it is not required to lock the buddy allocator. For page allocation, the same principle applies: The page is taken from the per-CPU list, so the buddy allocator does not have to be locked in that case either.

However, there are cases where the per-CPU list is insufficient: When a page should be allocated, but the list is empty, the buddy allocator is used to get a batch of pages, which requires locking the allocator for that allocation. The pages not required for the requested allocation are added to the per-CPU list so subsequent allocations can be handled with the pages in the list again. A similar principle applies when too many pages are in the list: Again, the buddy allocator is locked, and the pages from the list are returned to the buddy allocator.

In addition to the buddy allocator, the Slab allocator [24] is implemented on top of the buddy allocator. The Slab allocator allocates pages using the buddy allocator and provides them for allocating kernel objects. Since allocation and initialization of kernel objects would require much time when done directly via the buddy allocator, the Slab allocator keeps the allocated memory of the objects in an initialized state after they were freed. Thereby, the still allocated and pre-initialized memory can be used again when the next object of the same type is requested, which reduces the access time significantly. See Figure 3 for an overview of the memory allocation process.

<sup>&</sup>lt;sup>2</sup>amd64 architecture with 32 GiB of DRAM

Figure 3: Overview of the memory management of Linux. All allocation mechanisms are based on the buddy allocator. Different higher-level mechanisms, e.g. the Slab allocator or vmalloc(), abstract the usage of the buddy allocator. The MMU does the mapping between virtual and physical addresses. The mapping between physical and spatial addresses is done by the MC. The image was initially created by Prof. Dr. Florian Adamsky at HAW Hof.

#### 2.2 DRAM

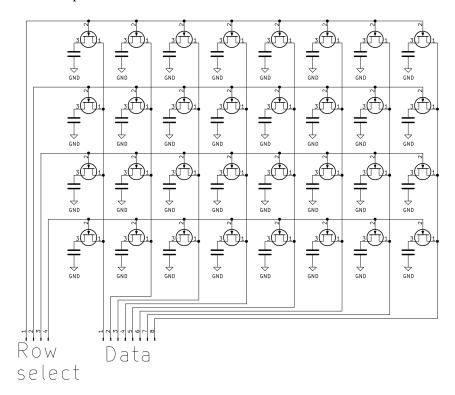

A DRAM cell consists of a capacitor and a transistor, as shown in Figure 4.

Figure 4: Single DRAM cell. One cell consists of a capacitor and a transistor. The image was created by myself as part of the practical thesis [21].

The capacitor stores the logical state in the form of an electrical charge. Depending on the electrical design of the cell, a discharged capacitor can be interpreted as logical 1 or logical 0. The cell is activated by applying a current to the pin depicted as 2 on the transistor. In that case, the transistor conducts and logically connects the pins depicted as 1 and 3.

In order to read the value that is currently stored in the cell, the voltage at the pin depicted as 1 is measured when the cell is activated. Writing to the cell works similarly: A voltage is applied at pin 1 while the cell is activated. If the applied voltage is  $V_{cc}$ , the capacitor is charged. If it is GND, the capacitor is discharged.

Reading the value of a DRAM cell discharges the capacitor. Therefore, it is required to restore the previous value after reading it (e.g. recharge the capacitor when it was charged before). Because the capacitor leaks charge over time, it is required to periodically recharge the cell, even if it was not accessed. On typical DDR3 and DDR4 systems, the DRAM cells are refreshed every 64 ms [30].

These DRAM cells are organized in an array of rows and columns, as shown in Figure 5. The access is always performed per row, meaning a row can only be activated completely. A row is activated by applying a voltage on the corresponding pin at the header labelled Row select in Figure 5. Depending on the access type (read or write), the charge of the capacitors can be measured or set at the pins labelled Data.

Figure 5: Array of DRAM cells. It is only possible to activate entire rows on the pins labelled *Row select*. When a row is activated, each cell within that row is electrically connected to one of the pins labelled *Data*. At these pins, the cells can be accessed as described for single cells, e.g. the charge can be measured to read the cells, or a charge can be applied to write to the cells. The image was created by myself as part of the practical thesis [21].

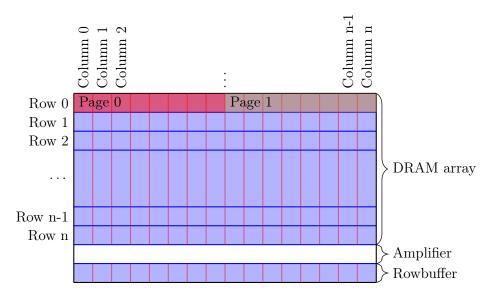

Because reading a row from the DRAM array destroys the data within the array, an additional buffer is required to cache the data until it is written back into the array. Since that buffer caches an entire row, it is called *row buffer*. There are amplifiers between the row buffer and the DRAM array. These components (DRAM array, amplifiers, and row buffer) are called a bank, as shown in Figure 6. Typically, one row within a bank has a size of 8 KiB so that it can fit two pages with a size of 4 KiB each. However, Pessl, Gruss, Maurice, *et al.* [7] showed that pages are not always

located in one bank but can be distributed over multiple banks.

Figure 6: DRAM Architecture: Bank. One DRAM bank consists of an array of DRAM cells, amplifiers, and a row buffer. Typically, one row has a size of 8 KiB so that it can fit two pages of 4 KiB. Depending on the addressing, two following pages can be in a row (as shown in the image). It is also possible that one page spans across multiple banks, which is often the case in multi-channel setups. As in the DRAM array depicted in Figure 5, it is only possible to activate entire rows. When a row should be read, it is activated, and its content is written into the row buffer. If a write operation is performed, the content of the row buffer is written into the row. The image was created by myself as part of the practical thesis [21].

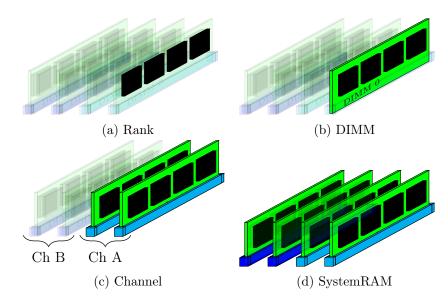

DRAM banks are distributed over the Integrated Circuits (ICs) that form a *rank*. There are layouts where one IC contains one bank, but there are also cases where one IC contains multiple banks or one bank is split across multiple ICs. Figure 7a shows one DRAM rank.

One or more ranks are part of a *DIMM* which is shown in Figure 7b. One or multiple DIMMs are at a bus connected to the CPU called *channel* shown in Figure 7c. There are systems with one or multiple channels. Everything together is the physical DRAM of the system shown in Figure 7d. Figure 7 depicts an overview of the different levels of the DRAM architecture described before.

As shown above, there is a row buffer with the size of a single row in each bank. When a row is read, its content is loaded into the row buffer and, at the same time, destroyed in the DRAM array. Afterwards, the data is not restored immediately but stays in the row buffer until another row is accessed. When that happens, the row buffer would be overwritten with the other row's content, resulting in a loss of the data currently stored in the row buffer (which was destroyed in the DRAM array when loaded into the row buffer). Therefore, the row buffer's content must be written back to the DRAM array before another row can be loaded into the row buffer.

There are two cases when data is read from DRAM: The requested row can already be in the row buffer, which is called *row hit*, or it can not be in the row buffer, which is called *row conflict*.

Figure 7: DRAM Architecture overview. The images were created by myself as part of the practical thesis [21].

When there is a row hit, the data can be directly returned without accessing the DRAM array. In the case of a row conflict, the current data in the row buffer has to be written first into the DRAM array. After that, the requested data is loaded into the row buffer. Then, the data can be returned from the row buffer.

#### 2.3 CPU CACHE

In order to increase the speed of accessing data, it is not always required to request it from DRAM, but it can be fetched from the CPU cache if stored in the cache. When read access to an address occurs, it is first checked if the data is already in the CPU cache (cache hit). If that is the case, the data is directly returned from the cache, and there is no access to the system DRAM. On the other hand, if the data is not in the cache (cache miss), the data is requested from DRAM. As described before, there can be a row hit or a row conflict in DRAM. In the case of a row hit, the data is returned faster than in the case of a row conflict.

Due to the differences in timing, it is possible to measure the access time and derive whether it was a cache hit, row hit, or row conflict based on the measured time.

In current CPUs, there are multiple levels of cache: Typically, the Level 1 (L1) and Level 2 (L2) caches belong to a CPU core and store only data accessed by that core. The Level 3 (L3) cache, also known as the Last Level Cache (LLC), is shared between all CPU cores [31]. There are different cache policies that specify whether data in one cache level must or must not be in other cache levels. Often, there is the *inclusive policy*, which means that data stored in the lower level

caches has to be stored in the higher level caches as well (e.g. data that is in the L1 cache has to be in the L2 cache and LLC as well).

#### 2.4 DRAM Address Functions

As described in Section 2.1, virtual addresses used by processes or the kernel are translated to physical addresses by the MMU. However, DRAM does not use physical addresses directly but is addressed spatially, e.g. by specifying the channel, DIMM, rank, bank, row, and column of the data. That translation between physical and spatial address is done by the MC that is integrated into the CPU in many modern systems.

The mapping between virtual and physical addresses can be obtained using the file /proc/self/pagemap [32] provided by the Linux kernel. However, to get the mapping from the physical address to a spatial one, it is required to know the mapping mechanisms implemented in the MC, which are not publicly available in many cases.

Often, it is not essential to get all spatial information, but some information can be abstracted. For example, on a system with 16 banks in total, it might be sufficient to know the number of the bank. It would not be required to have information about the rank in which the bank is organized, the DIMM the rank is on, and the channel the DIMM is connected to, as long as all banks have a continuous number (e.g. bank 0 to bank 15).

As described in Section 2.3, it is possible to use the access timing information to derive whether an access was a cache hit, a row hit, or a row conflict. When two addresses are accessed alternately and removed from the CPU cache before each access, there are only two possibilities: The access can be fast (which would indicate a row hit) or slow (which would indicate a row conflict). Since DRAM needs to be refreshed and other processes access the DRAM simultaneously, there is some noise in the measurement. However, when that measurement is repeated several times, there are clear timing differences between two addresses accessed with row hits or row conflicts.

In a spatial view, a row hit means that the addresses are either in different banks (because each bank has its own row buffer that stores the row that was last accessed) or at the same bank and in the same row (because the row buffer of that bank stores always the same row). When there is a row conflict, the addresses have to be on the same bank and in different rows because access to another row requires the current content of the row buffer to be written back to the DRAM array before the next row can be loaded into the row buffer.

When there are enough physical addresses grouped by spatial banks, it is possible to calculate the address function for the banks: The number of banks is a power of 2, so there are  $log_2(n)$  bits required to address n banks. Each bit of the bank number is calculated by applying XOR to the physical address and the address mask. Afterwards, XOR is applied to that value: when there is an even number of ones, the result is 0. If the number of ones is odd, the result is 1 [7], for example:

| Mask (binary)                           | Result (Physical Address XOR Mask)      | Result Bit |

|-----------------------------------------|-----------------------------------------|------------|

| 000000000000000001000000000000000000000 | 000000000000000000000000000000000000000 | 0          |

| 000000000000100100000000000000000000000 | 000000000000000000000000000000000000000 | 0          |

| 000000000000010010000000000000000000000 | 000000000000000100000000000000000000000 | 1          |

| 000000000001001000000000000000000000000 | 000000000001001000000000000000000000000 | 0          |

In that example, the binary result of the number of the bank would be 0010, which is equal to 2. However, it should be noted that there is no additional information about the order of the masks, so depending on that arbitrarily chosen order, the bank number might be any combination of the result bits. However, it is possible to calculate if two physical addresses are within the same bank when an arbitrarily chosen but fixed order is used.

It should be noted that, as stated before, pages are not always stored in one row but can span across multiple rows [7]. Therefore, a sufficient resolution of the addresses used in the first stage of grouping them by the bank they belong to is required. Depending on the system, it might not be sufficient to use only the base address of each page (e.g. setting the last 12 bit of the physical address to 0).

Based on the address information about the banks, row adjacency can be guessed: When a sequence of physical addresses is grouped by banks, they are in the same row within that bank as long as the bank stays the same (e.g. bank 2). When the bank changes (e.g. bank 4), the same principle also applies to that bank. The data is in the next row when the bank is the same one as before again (e.g. bank 2). As shown by Cojocar, Kim, Patel, et al. [33], the mapping of the physical address to the spatial rows is not always linear, so the approach of guessing the row information is not always correct. Because there is no good way to measure row adjacency in software, the authors built a hardware fault injector to get information about row adjacency.

To conclude: It is possible to reverse engineer the used address functions to calculate the bank number from a physical address in software without requiring additional hardware. That approach works as well when a physical page spans multiple banks. However, it does not provide semantic information about the calculated bits (e.g. which bit specifies the rank, which specifies the DIMM, etc.) In contrast, there is no good way to reverse engineer spatial information about the rows in software: Additional hardware is required. It is still possible to guess spatial row information, which might not be correct.

#### 2.5 ROWHAMMER

As stated in Section 2.2, a bank in DRAM consists of an array of DRAM cells, amplifiers, and row buffer. Depending on the current content in the row buffer, there can be a row hit (requested data is already in the row buffer) or a row conflict (requested data is not in the row buffer). In

the case of a row conflict, the row buffer data must be written to the DRAM array to avoid data loss.

Reading data from or writing data to the DRAM array is based on electrical currents flowing from or into the DRAM cells. Those currents can lead to disturbance errors in nearby cells by leaking charge from or into the capacitors of these cells. If that leaked charge is strong enough, so the capacitor charge level is interpreted as *full* when it was *empty* before or the other way around at the next refresh of the cell, the bit stored in the cell *flipped*: A logical 1 became a logical 0, or a logical 0 became a logical 1.

Within normal operation, that case should not happen because that would result in memory errors everywhere. Therefore, the cells are designed so that typical operations do not (or not often) lead to the effect described above. However, the physical problem does still exist.

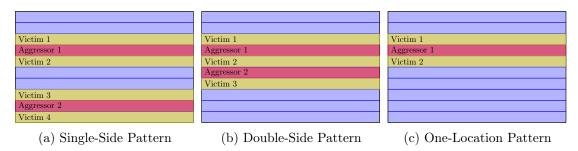

Rowhammer is the approach to exploit these effects actively by using specific access patterns that maximize the number of such bit flips. An access pattern consists of a list of aggressor rows that are read and a list of victim rows that might contain bit flips after the aggressor rows were read several times. Reading the aggressor rows sequentially is called hammering. Because the charge of the capacitors is restored at each refresh, the aggressors should be hammered for two refresh cycles so that there is at least one complete cycle. There are statically defined patterns, such as those shown in Figure 8.

Figure 8: Some typical patterns for Rowhammer exploitation. The *Aggressors* are the rows accessed alternatingly and, thereby, loaded into and restored from the row buffer. The *Victims* are the rows that will likely show flipped bits after a sufficiently high amount of accesses to the *Aggressors*. The images were created by myself as part of the practical thesis [21].

In 2015, Seaborn and Dullien [2] published an exploit that uses Rowhammer to flip bits in PTEs and, thereby, get a PTE to point to the physical address of another PTE. It is possible to use the virtual address mapped by the manipulated PTE to write a PTE currently mapped into the process's address space. Due to that, the attacker can map arbitrary physical addresses into the virtual address space of its own process, which means that he can arbitrarily read and write the system's entire memory.

Their exploit demonstrated that Rowhammer is not a purely academic problem but can also be used for the exploitation of productive systems. At that time, vendors started to develop and roll

out mitigations against Rowhammer. One of the first mitigations was to double the refresh rate since the accesses have to be done between two refreshes. With a double refresh rate, this results in half the number of possible accesses between two refreshes.

Another mitigation approach is to detect if a Rowhammer attack is running, find the victim rows and refresh them. Initially, that was done by the MC: Each DDR3 DIMM has an entry in its Serial Presence Detect (SPD)<sup>3</sup> how many activations require a refresh. That approach is called pseudo Target Row Refresh (pTRR). In DDR4, a similar approach can be directly implemented at the DIMM. In that case, the refresh is done by the DIMM and not by the MC.

It was assumed that Error Correction Code (ECC) DRAM is not affected by Rowhammer because single-bit flips should be automatically detected and corrected. However, as shown by Cojocar, Razavi, Giuffrida, et al. [14], that assumption was wrong, and it is possible to exploit Rowhammer on ECC DRAM.

Kim, Daly, Kim, et al. [1] mentioned that a double refresh rate does not fully mitigate Rowhammer. As shown in my practical [21] and bachelor's [22] theses, other mechanisms, in detail parallel hammering and execution of an additional sequence of x86 instructions (together called flipper), can be used to increase the number of bit flips found in a given time significantly. Depending on the DIMM, such mechanisms can render the mitigation of a double refresh rate useless (the number of bit flips in a given time on a system without mitigation is equal to the number of bit flips on the same system with the mitigation and amplification).

Because pTRR and Target Row Refresh (TRR) rely on detecting Rowhammer patterns, it would be required to find a pattern that induces bit flips without being detected by the implementation of pTRR or TRR. However, new approaches to bypass these mitigations [15], [17], [19], [20] have been published in recent years.

<sup>&</sup>lt;sup>3</sup>Electrically Erasable Programmable Read-Only Memory (EEPROM) on the DIMM that stores information about the DIMM which is read by the Basic Input/Output System (BIOS) at initialization time. SPD [34], [35] can be accessed from the OS as well.

# 3 FLIPPER ON DDR4

As mentioned before, *flipper* [21], [22], the approach that increases the number of bit flips found in a given time by a hundredfold [22], was only evaluated on DDR3 DRAM due to hardware limitations<sup>4</sup> when the experiments were performed.

Within this thesis, there is a test setup with two systems and 60 DDR4 DIMMs with 8 GiB each. Therefore, the experiments done before can be repeated on those systems to verify if flipper increases the number of bit flips found in a given time on DDR4 the same way it does on DDR3.

If no bit flips are found, it is not certain if the PoC does not work or if the system is not affected by Rowhammer. For that reason, the PoC published by Jattke, van der Veen, Frigo, et al. [17] was used to scan all 60 DIMMs first. That PoC was chosen because the authors claim to have found bit flips on 40 out of 40 tested DDR4 DIMMs.

In the following sections, the automated test setup used for those experiments is described in detail, and the results of the experiments are shown.

#### 3.1 AUTOMATED TEST SETUP

I have developed an ISO image based on Archiso [36] to perform automated Rowhammer experiments in the scope of the practical [21] and bachelor's [22] theses. The usage of such a setup brings multiple benefits:

- It is not required to install a test system (e.g. install the required software, adjust the configuration, etc.).

- The software versions on all systems are the same over the entire experiment, even if the systems are used for other tasks and, for that reason, updated regularly.

- Most parts of the experiments can be automated to minimize the effort required to perform them.

- Due to the reduced manual interaction, the experiments are less prone to errors made by humans and are performed precisely the same way for each iteration.

Initially, the setup was meant to perform the experiments on any system that boots the ISO image. After the experiments are done, they are uploaded to a server to analyze the results. That mode of operation is called *remote mode* in the current version. In addition, a *local mode* connects to a shared storage (in the current version, *sshfs* [37] is used for that). Thereby it is possible to have a shared state over multiple systems and reboots. The Media Access Control (MAC)

<sup>&</sup>lt;sup>4</sup>There were two systems with DDR4 DRAM. One had an AMD CPU, so the implemented approach of reverse engineering the address functions did not work [22]. The other one did not seem to be affected by Rowhammer.

#### 3 Flipper on DDR4

address of the primary Network Interface Controller (NIC) is used to distinguish the systems on which the experiments are performed.

For the experiments, 60 DIMMs were tested on two systems. First, it is required to map the physical DIMM to the result set which was uploaded. That is done by physically labelling the DIMMs (D4M01 — D4M60). Afterwards, a state file in the shared storage is created for each system. The file is named like the MAC address of the system in the shared storage. Each file contains the number of the DIMM that will be tested next and the step width, which was two for the experiment.

During execution, the number of the next DIMM is written to the file after the data is successfully uploaded. Due to that, it is only required to plug in the next DIMM and start the system. Afterwards, the experiments are executed automatically. Finally, the system was powered off if everything was successful, and the DIMM could be replaced.

The initially generated ISO image was specially adjusted to match the requirements of the experiments at that time. However, due to that, the architecture made it hard to extend the experiments. For that reason, the architecture was adjusted in order to make it easier to add new experiments.

In the current architecture, there are four stages:

- Collect Information: General system-wide information about the CPU, DIMMs, SPD, etc., is collected.

- Reverse Engineering of the Address Functions: The address functions are reverseengineered, as described in Section 2.4.

- Execution of Experiments: Depending on the PoC, it might be required to adjust the source code and recompile it if the address functions are hard coded. It might also be required to modify a configuration file or adjust command-line parameters. After that, the PoCs are executed.

- Evaluation of Results: The results (e.g. the number of bit flips) are evaluated and, in the end, printed in a brief overview.

Based on that architecture and the features of Bash [38], adding a new PoC requires the creation of a new file, myExperiment.sh, in the Scripts/PoCModules directory. An example file is shown in Listing 1

```

#!/bin/sh

setvar_MyExperiment() {

# Define the name of the PoC

POCNAME="New PoC"

# Define the number of iterations (e.g. how often the experiment is executed)

```

```

# If that number is greater than 1, there should be a loop in the

9

# measure_MyExperiment function that calls Set_Step before each execution.

10

# This is used to update the percentage display after each execution and get

11

# a more precise forecast about the time required until finished.

12

POCITERATIONS=1

13

}

14

15

init_MyExperiment() {

# Build the PoC only when it was not already built (depending on the

16

17

# experiment configuration multiple experiments can share the same PoC and run

# it with different parameters).

18

if [ "$BUILT_MyPoC" != "Y" ]; then

19

cd PoC/mypoc && make; cd ../..

20

export $BUILT_MyPoC="Y"

21

22

fi

23

24

# If Hugepage support is required, it should be enabled if not already enabled

25

# by another experiment file.

26

if [ "$BUILT_HugePage" != "Y" ]; then

27

sh ./PoC/trrespass/hugepage.sh

28

export BUILT_HugePage="Y"

29

fi

30

}

31

32

measure_MyExperiment() {

33

# Perform the actual measurement by executing the PoC. Use the TIMEOUT

34

# variable in a way that the PoC terminates after that time. This can be done

# with timeout as shown below, or with something else. It is only important

35

# that the PoC terminates after that time.

36

# Additional, there is the LOGDIR variable that specifies the directory where

37

38

# all experiment logs are stored. Make sure that all files the PoC creates are

39

# stored in that directory.

(time timeout -s SIGINT $TIMEOUT ./PoC/mypoc/mypoc) 2>&1 | \

40

41

tee $LOGDIR/MyExperiment.log

}

42

43

44

eval_MyExperiment() {

45

# Perform the evaluation of the experiment by counting the number of bit flips

46

# that occurred from the log file created before. Write the result to a file

47

# in EVALDIR.

48

cat $LOGDIR/MyExperiment.log | grep flip | wc -1 > $EVALDIR/MyExperiment.txt

49

}

50

51

print_MyExperiment() {

52

# Print the number of bit flips found that was calculated in the eval

# function. Normally, it should be sufficient to just print the content of the

53

54

# file in the EVALDIR directory.

echo "MyExperiment: $(cat $EVALDIR/MyExperiment.txt)"

55

56

}

```

Listing 1: Example of a file describing an experiment for the test setup.

#### 3 Flipper on DDR4

After the experiment definition file is created, it is required to enable the experiment. This can be done by editing the files Scripts/localConfig.sh and Scripts/remoteConfig.sh. Add lines with the content shown in Listing 2 to enable the experiment. The entry in the configuration must have the same name as the file created before because the experiment is matched by the file's name.

```

BASELINE_MyExperiment="Y"

FLIPPER_MyExperiment="Y"

```

Listing 2: Lines to enable the experiment created before

More information about the automated test setup can be found in Section A.2.

#### 3.2 BlackSmith Experiment

In order to find the DIMMs most susceptible to Rowhammer, the BLACKSMITH PoC [17] introduced by Jattke, van der Veen, Frigo, et al. is executed on 60 DIMMs using the ISO image described in Section 3.1. Two identical test systems with an Intel(R) Core(TM) i9-10900K CPU are used for the experiment. For reference, the systems are named hammertest01 and hammertest02. The DIMMs are labelled for reference (D4M01 - D4M60). The ones with odd numbers are tested on hammertest01, and those with even numbers on hammertest02. Each DIMM is tested for a total time of 6 h.

The publication [17] states that 40 out of 40 DDR4 DIMMs were susceptible to Rowhammer. The authors tested  $256 \,\mathrm{MiB}$  of memory for each DIMM and measured an average amount of 720.45 bit flips. For that reason, it was decided to use that PoC because the results from the paper looked promising. Therefore, it was assumed that the PoC should find bit flips on a DIMM when it is susceptible to Rowhammer.

In addition to the number of bit flips, the authors measured the time until the first exploitable bit flip occurred. As stated before, a bit flip is considered to be exploitable when it occurred at a specific offset within a page that could be exploited if the page was used accordingly. In the case of the publication, the exploitation of PTEs, RSA-2048 and sudo was analyzed. The longest time measured was 4 h 2 min for an offset that could be exploited with RSA-2048. Since 34 of 40 DIMMs had exploitable bit flips (which are a subset of the bit flips found in total) within that time it was assumed that 6 h should be sufficient to find bit flips on most DIMMs.

However, bit flips are only found on 4 out of 60 DIMMs during the evaluation. So, the results from the paper can not be reproduced with the test setup used for that experiment. Table 1 lists the details of the DIMMs that are affected. On all other DIMMs, no bit flips were found within the tested time frame of 6 h.

As shown in Table 1, only DIMMs with odd numbers are affected by Rowhammer. Due to the test setup, all those DIMMs were tested with *hammertest01*. Therefore, it is evaluated if these results can be reproduced on *hammertest02* to exclude a problem with the test setup.

| Module ID | Number of Bit flips |

|-----------|---------------------|

| D4M001    | 9                   |

| D4M021    | 6                   |

| D4M037    | 4                   |

| D4M043    | 2                   |

Table 1: Number of Bit Flips found within 6 hours by the BlackSmith PoC without flipper

It was not possible to reproduce the results measured on hammertest01 with the same DIMMs on hammertest02, so bit flips did only occur when a DIMM was tested on hammertest01. Since hammertest01 and hammertest02 have identical hardware and the same BIOS version, that is a strange effect. Because there was not enough time to analyze this further in the scope of this master thesis, it is suggested to inspect that behaviour in the future. See Section 6 for a description of what should be analyzed concerning that effect.

The DIMMs with bit flip were tested with the current version of the PoC hammertest [21]. However, no bit flips were found during those tests. That was expected since hammertest implements classical Rowhammer patterns that are not TRR aware.

Because the experiment results show that none of the tested DIMMs is strongly susceptible to Rowhammer, it is decided to skip further experiments. Instead, it is focused on the process-based Rowhammer exploitation described in Section 4.

# 4 EXPLOITATION APPROACH

As shown by Gruss, Lipp, Schwarz, et al. [11], it is possible to use Rowhammer to exploit the page cache, a caching mechanism that stores the content of files in memory to increase access speed. In detail, an executable binary, library, etc. is loaded into the page cache before execution. If the files on disc were not modified since the last execution and the data is already in the page cache, furthermore executions access the binary directly via the page cache.

The authors target the *opcodes* of userspace binaries stored in the page cache by flipping bits in the instructions. Thereby, the targeted instructions are changed and the binary executes the modified instructions resulting in a change of executed instructions. If that attack is performed on a binary which is executed by the root user since the permissions are set accordingly, it is possible to escalate privileges by executing modified instructions as root.

In addition to exploiting a userspace binary by flipping bits in the opcodes stored in the page cache, it should be possible to flip bits in the memory used at runtime. In the *templating phase*, the attacker's process allocates memory and scans it for bit flips by executing Rowhammer. If a vulnerable page is found, that page is freed so that it is allocated by another process spawned by the attacker at a specific offset in the *reallocation phase*. After that process has started, the bit flip can be triggered again in the *attacking phase* by accessing the aggressor rows that induced the bit flip during templating. The child process should have some wait condition (e.g. waiting for user input) for that approach to work reliably. If the bit flip was induced again, it occurred in the memory used by the child process. A graphical representation of that exploitation approach is shown in Figure 9.

Suppose it is possible to get the vulnerable page remapped in the spawned process at a location chosen by the attacker. In that case, it should be possible to flip bits in arbitrary pages for arbitrary binaries. However, if there is no wait condition within the binary, there is the additional challenge of performing the Rowhammer attack at the correct time. When that happens with a binary where the Set User IDentification (SUID) bit is set, an attacker can modify variables in the binary's memory. If the correct variables are modified, it should be possible to change the control flow of the process and escalate the attacker's privileges.

# Scan Memory Free Victim Page Spawn Victim Process Victim Process Allocate Memory Initialize Memory Wait Perform Rowhammer Continue

Figure 9: Exploitation approach for attacking process memory. The steps of the *templating phase* are shown in green, the steps of the *reallocation phase* in blue, and the steps of the *attacking phase* in red.

# 4.1 Hybrid Grouping

Attacker Process

As shown in Section 2.1, virtual addresses are mapped to physical addresses using page tables. These mappings can be accessed in Linux by reading the file /proc/PID/pagemap, where PID is the ID of the process whose mappings should be inspected. However, access to the mappings is restricted to users with the  $CAP\_SYS\_ADMIN$  privilege to avoid Rowhammer exploitation [39]. This problem can be partly solved by using THP since the last 9 bit of the PFN are directly mapped, e.g. the same for the virtual and the physical address. Thereby, the last 9 bit of the PFN are known.

However, it is impossible to free single pages from a THP, so they are allocated again by another process. A short test implementation<sup>5</sup> shows that single pages can be freed using, for example, madvise [28] with the *MADV\_DONTNEED* flag or *munmap* [29]. However, they are not allocated to another process until there is an Out Of Memory (OOM) condition and, thereby, the parent

<sup>&</sup>lt;sup>5</sup>A THP is allocated using mmap() and madvise(), afterwards a single page of that THP is freed using either munmap() or madvise(). Then, a write access is performed to the virtual address. During that, the PFN is retrieved from the pagemap file in procfs. After the allocation, there is a PFN at the virtual address. After freeing the page, the PFN is 0x00. When the write access took place, there is another PFN that is different than the one before.

process is killed. That behaviour was measured with another short experiment<sup>6</sup>. Afterwards, the experiment was slightly modified by killing the parent process manually which led to the reallocation of some freed pages as well.

Because the exploitation approach described before needs both: Correct groups of addresses for the Rowhammer exploitation and the possibility to free single pages afterwards, there was the requirement to find a new approach for grouping the virtual addresses.

The trivial approach would be to group all addresses manually, e.g. create a list of addresses per bank and measure the access times of the addresses against n addresses of each group. Since there should be row conflicts when the addresses are in the same bank, the address is added to the group with the slowest access time afterwards. However, many measurements are required for this approach which, therefore, is pretty slow.

Since the address functions are still used by the MC but can not be applied directly to virtual addresses, another approach is to mix both mechanisms: Perform time-based measurements where necessary and use address function related effects where possible.

As stated in Section 2.1, the buddy allocator handles blocks of  $2^n$  physically continuous pages where n is called the *order* of that block. The numbers of the banks in which these addresses are have to follow the address functions implemented in the MC. If it is known which order the current block from the buddy allocator has and how the addresses are grouped based on the address functions, most banks could be mapped using the address functions. The number of required measurements is reduced significantly, leading to faster results.

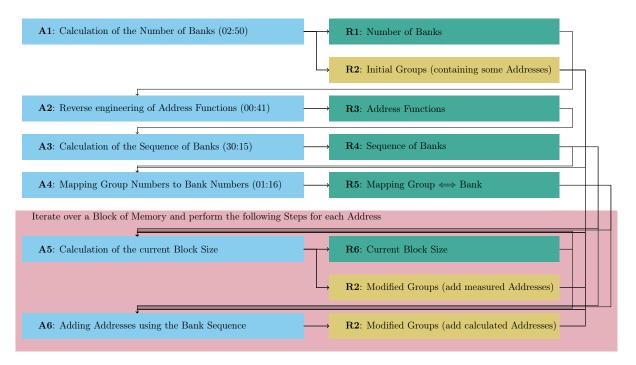

HYBRIDGROUPING is an approach that combines manual measurements with knowledge about the addressing functions. Figure 10 shows an overview of that approach. In the following, the different steps are explained in detail.

<sup>&</sup>lt;sup>6</sup>One parent process allocated multiple THPs and freed single pages out of it using munmap [29]. Afterwards, it spawned child processes that allocate pages, write to them, and verify if the allocated pages have one of the freed PFNs. It showed that that was just the case after an OOM condition occurred and the parent process was killed.

Figure 10: Overview of the Hybridgrouping approach. On the left side, the different Actions performed by the PoC are depicted in blue. The right side shows the Results of those steps. The groups that contain virtual addresses by bank and, therefore, are the final result are depicted in yellow. Intermediate results are depicted in green. The depicted times the different actions require are rough estimations measured on one system (average over 5 measurements). It should be noted that the required time depends strongly on the parameters of the PoC and the system it is executed on.

### A1: CALCULATION OF THE NUMBER OF BANKS

A threshold time between row hit and row conflict is calculated in the beginning. This is done by allocating a block of memory and comparing the first address in the block with every other address. Two addresses are compared by reading them multiple times (e.g. 1000 times<sup>7</sup> for the Hybrid approach) alternatingly and flushing the data from the cache afterwards. Thereby, each read results in access to the DRAM. During the read sequence, the time is measured. There should be many address pairs with a *fast* access time and some address pairs with a *slow* access time. Based on that, the threshold is calculated as the average of the median *fast* and the median *slow* access time.

The number of banks is calculated by creating an initially empty list of address groups. After that, a block of memory<sup>8</sup> is allocated, and each address of that block is compared to n addresses randomly chosen from each existing address group. Multiple addresses are compared one after

<sup>&</sup>lt;sup>7</sup>A higher amount of measurements increases the accuracy and the time that is required to measure. 1000 is a good compromise on the systems the experiment was performed on.

$<sup>^8</sup>$ In the current implementation, 512 pages (2 MiB) are used. Since the system the tests were performed on has 16 banks, there is an average 32 addresses in each group, which yielded good results during experimentation.

another. In the end, the median access time is taken as a result. Because the pages do not span multiple banks on the test system, it is sufficient to use only the virtual addresses at a page border (e.g. where the last 12 bit are zero).

When there are address groups with a median access time bigger than the threshold calculated, the address is added to the group with the biggest access time. Due to noise in the system, multiple groups with an access time bigger than the threshold might exist. However, the access time to the correct group should be the biggest). If no group has an access time bigger than the threshold, a new group is created, and the address is added to that group.

Because a row within a bank has a size of 8 KiB, it can store 2 pages with a size of 4 KiB each. For that reason, two pages can be in the same bank and the same row if pages do not span multiple banks, which is the case on the test system. Often, this happens to pages physically following each other. Because both pages are in the same bank and row, there is a row hit in that case, so the second page is added to a newly created group. That problem can be solved by adding a regrouping step. First, each group is removed (one after another) from the list of groups. Afterwards, the addresses of the removed group are added one after another, as described before. Finally, insignificantly small groups are removed (e.g. groups that contain fewer addresses than  $\frac{1}{n}$  of the median of all groups, in the current version, less than  $\frac{1}{4}$ ).

Afterwards, the number of groups should equal the number of banks in the system (which should be a power of 2). Additionally, the groups contain some addresses. Therefore the effect of wrong grouping because two addresses are in the same bank and the same row (as described above) should not happen anymore.

### A2: Reverse engineering of Address Functions

The reverse engineering of the address functions is done using HammerliB, a Rowhammer library written as a part of my practical thesis [21]. The basic approach of reverse engineering DRAM address functions is described in Section 2.4.

# A3: CALCULATION OF THE SEQUENCE OF BANKS

Because the PFNs of the addresses can not be resolved without root privileges, it is not possible to apply the address functions directly to the PFNs. However, applying the address functions to addresses that follow each other results in a *sequence of banks* that repeats itself. That sequence is used for the calculating of the current block size as described at A5: Calculation of the current Block Size and for adding the addresses to the correct groups as described at A6: Adding Addresses using Bank Sequence.

The sequence contains the bank numbers for a hypothetical PFN ( $0 \le PFN < x$ ), where x is the unique length of the sequence before it repeats itself. It is generated by assuming the hypothetical

PFN to be 0 in the beginning and calculating the number of the bank using the address functions as described in Section 2.4. Afterwards, the hypothetical PFN is increased to be 1, etc., until it is equal to x. Figure 11 depicts such a bank sequence with a length of 512.

| 0 | 0 8  | 8  | 2 | 2 | 10 | 10 | 4 | 4 | 12 | 12 | 6 | 6 | 14 | 14 | 1 | 1 | 9  | 9  | 3 | 3 | 11 | 11 | 5 | 5 | 13 | 13 | 7 | 7 | 15 | 15 |

|---|------|----|---|---|----|----|---|---|----|----|---|---|----|----|---|---|----|----|---|---|----|----|---|---|----|----|---|---|----|----|

| 2 | 2 10 | 10 | 0 | 0 | 8  | 8  | 6 | 6 | 14 | 14 | 4 | 4 | 12 | 12 | 3 | 3 | 11 | 11 | 1 | 1 | 9  | 9  | 7 | 7 | 15 | 15 | 5 | 5 | 13 | 13 |

| 4 | 4 12 | 12 | 6 | 6 | 14 | 14 | 0 | 0 | 8  | 8  | 2 | 2 | 10 | 10 | 5 | 5 | 13 | 13 | 7 | 7 | 15 | 15 | 1 | 1 | 9  | 9  | 3 | 3 | 11 | 11 |

| 6 | 6 14 | 14 | 4 | 4 | 12 | 12 | 2 | 2 | 10 | 10 | 0 | 0 | 8  | 8  | 7 | 7 | 15 | 15 | 5 | 5 | 13 | 13 | 3 | 3 | 11 | 11 | 1 | 1 | 9  | 9  |

| 1 | 1 9  | 9  | 3 | 3 | 11 | 11 | 5 | 5 | 13 | 13 | 7 | 7 | 15 | 15 | 0 | 0 | 8  | 8  | 2 | 2 | 10 | 10 | 4 | 4 | 12 | 12 | 6 | 6 | 14 | 14 |

| 3 | 3 11 | 11 | 1 | 1 | 9  | 9  | 7 | 7 | 15 | 15 | 5 | 5 | 13 | 13 | 2 | 2 | 10 | 10 | 0 | 0 | 8  | 8  | 6 | 6 | 14 | 14 | 4 | 4 | 12 | 12 |

| 5 | 5 13 | 13 | 7 | 7 | 15 | 15 | 1 | 1 | 9  | 9  | 3 | 3 | 11 | 11 | 4 | 4 | 12 | 12 | 6 | 6 | 14 | 14 | 0 | 0 | 8  | 8  | 2 | 2 | 10 | 10 |

| 7 | 7 15 | 15 | 5 | 5 | 13 | 13 | 3 | 3 | 11 | 11 | 1 | 1 | 9  | 9  | 6 | 6 | 14 | 14 | 4 | 4 | 12 | 12 | 2 | 2 | 10 | 10 | 0 | 0 | 8  | 8  |

| 0 | 0 8  | 8  | 2 | 2 | 10 | 10 | 4 | 4 | 12 | 12 | 6 | 6 | 14 | 14 | 1 | 1 | 9  | 9  | 3 | 3 | 11 | 11 | 5 | 5 | 13 | 13 | 7 | 7 | 15 | 15 |

| 2 | 2 10 | 10 | 0 | 0 | 8  | 8  | 6 | 6 | 14 | 14 | 4 | 4 | 12 | 12 | 3 | 3 | 11 | 11 | 1 | 1 | 9  | 9  | 7 | 7 | 15 | 15 | 5 | 5 | 13 | 13 |

| 4 | 4 12 | 12 | 6 | 6 | 14 | 14 | 0 | 0 | 8  | 8  | 2 | 2 | 10 | 10 | 5 | 5 | 13 | 13 | 7 | 7 | 15 | 15 | 1 | 1 | 9  | 9  | 3 | 3 | 11 | 11 |

| 6 | 6 14 | 14 | 4 | 4 | 12 | 12 | 2 | 2 | 10 | 10 | 0 | 0 | 8  | 8  | 7 | 7 | 15 | 15 | 5 | 5 | 13 | 13 | 3 | 3 | 11 | 11 | 1 | 1 | 9  | 9  |

| 1 | 1 9  | 9  | 3 | 3 | 11 | 11 | 5 | 5 | 13 | 13 | 7 | 7 | 15 | 15 | 0 | 0 | 8  | 8  | 2 | 2 | 10 | 10 | 4 | 4 | 12 | 12 | 6 | 6 | 14 | 14 |

| 3 | 3 11 | 11 | 1 | 1 | 9  | 9  | 7 | 7 | 15 | 15 | 5 | 5 | 13 | 13 | 2 | 2 | 10 | 10 | 0 | 0 | 8  | 8  | 6 | 6 | 14 | 14 | 4 | 4 | 12 | 12 |

| 5 | 5 13 | 13 | 7 | 7 | 15 | 15 | 1 | 1 | 9  | 9  | 3 | 3 | 11 | 11 | 4 | 4 | 12 | 12 | 6 | 6 | 14 | 14 | 0 | 0 | 8  | 8  | 2 | 2 | 10 | 10 |

| 7 | 7 15 | 15 | 5 | 5 | 13 | 13 | 3 | 3 | 11 | 11 | 1 | 1 | 9  | 9  | 6 | 6 | 14 | 14 | 4 | 4 | 12 | 12 | 2 | 2 | 10 | 10 | 0 | 0 | 8  | 8  |

Figure 11: Example of the usage of bank sequences. The current block size is 8, and the offset is 0. The fields in red are the measured offsets, the blue one is the verification offset, and the green ones are additional fields in the block that have not to be measured. The block itself can be seen as a sliding window that is shifted over the bank sequence until the measured offsets (in red) and verification offset (in blue) match the measurement. If no valid sub-sequence is found within the sequence, the block size is reduced, and the procedure is repeated (with a block size of 4). At the same time, the procedure is performed for double the current block size (in this example 16). If the requirements described above are met, the block size is doubled.

As stated before, the pages do not span multiple banks on the test systems, so using the base addresses for each hypothetical PFN (e.g. append 12 bit with a value of zero) works. However, on other systems where the pages do span multiple banks, it is required to add multiple offset addresses depending on the exact span of the pages over the banks (e.g. when a page spans over 8 banks, 8 addresses have to be calculated for each hypothetical PFN with the corresponding offsets).

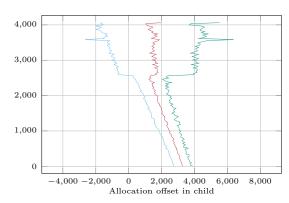

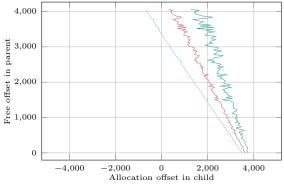

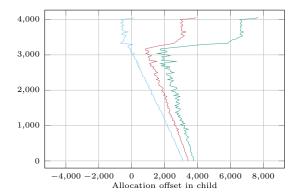

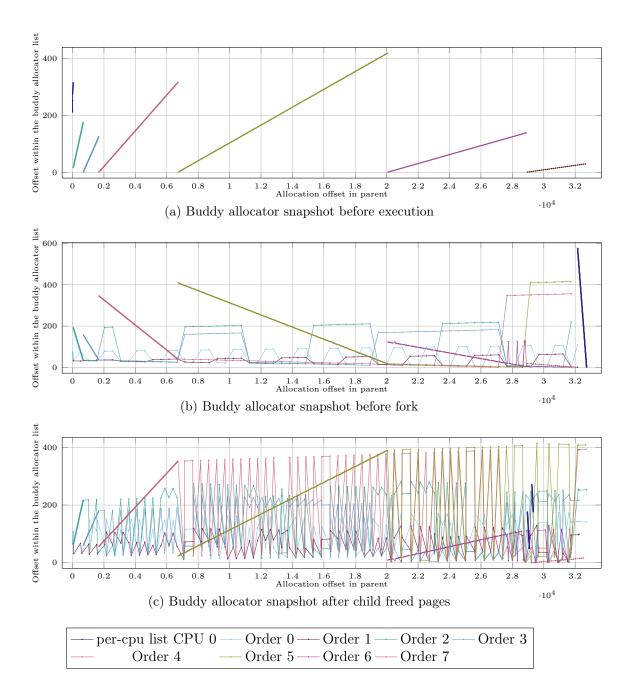

The result of this calculation is a sequence of bank numbers that matches for addresses following each other. When n PFNs are physically continuous, there has to be at least one sub-sequence of length n with matching bank numbers. In Figure 11, the sub-sequence is depicted as the colored part (e.g. the first eight items in the sequence).